# Introduction Control system setup

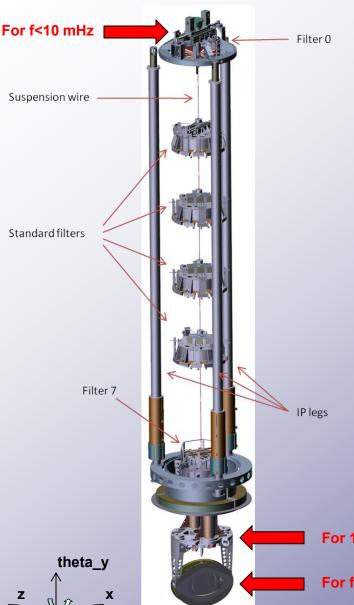

The control system has been designed using a hierarchical strategy regulated by the dynamic range of the actuators.

- 23 Coil Magnet Actuators in 3 points (actuation stages) of the SA:

- Filter 0:

Large displacements (hundreds of microns) for f<10 mHz.

- Filter 7 + Marionette:

Small payload displacements (1 micron) in the 10 mHz<f<1 Hz band.

- Filter 7 + Mirror:

Small residual mirror displacements (a few nm), for f>1 Hz.

- >20 Local Sensors

- Accelerometers

- 4 Displacements Sensors (LVDTs) on Filter 0

- 6 Displacements Sensors on Filter 0

- Optical Readout of Marionette and Mirror Position

- Digital Control system based on high-performance multicore DSPs.

For 10 mHz<f<1 Hz

For f>1 Hz

### Introduction Control system setup

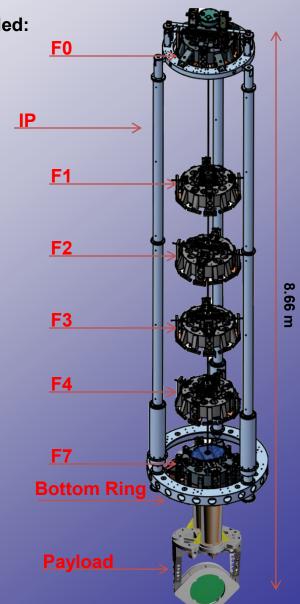

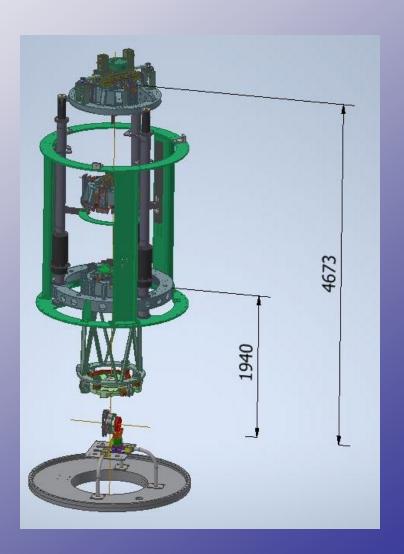

On long superattenuators (BS, NI, NE, WI, WE, PR, SR) are installed:

- 18 LVDTs of 3 different types

- 9 Vertical LVDTs (F0 F7 Crossbar, Bottom Ring)

- 3 F0 Horizontal LVDT

- 6 F7 LVDTs

- 5 Accelerometers of 2 different types installed on F0:

- 3 Horizontal Accs

- 2 Vertical Accs

- 23 Coils of 4 different types

- 5 F0 Coils

- 6 F7 Coils

- 8 Marionette coils

- 4 Mirror coils

- 3 Piezos on bottom ring (Not uset yet)

- 21 Motors

- 1 Top screw F0 vertical motor

- 3 F0 trolley motors

- 6 Fishing rod motors

- 2 Marionette motors

- 4 F7 motors

- 5 Accelerometer motors

#### On IB superattenuator are installed:

- 9 LVDTs of 2 different types

- 6 Vertical LVDTs (F0, F4, F7 Crossbar, Bottom Ring)

- 3 F0 Horizontal LVDT

- 5 Accelerometers of 2 different types installed on F0:

- 3 Horizontal Accs

- 2 Vertical Accs

- 13 Coils of 2 different types

- 5 F0 Coils

- 8 Marionette coils

- 3 Piezos on bottom ring (Not used yet)

- 18 Motors

- 1 Top screw F0 vertical motor

- 3 F0 trolley motors

- 3 Fishing rod motors

- 2 Marionette motors

- 4 F7 motors

- 5 Accelerometer motors

# **Introduction**Control system setup

#### On MC superattenuator are installed:

- 9 LVDTs of 2 different types

- 6 Vertical LVDTs (F0, F4, F7 Crossbar, Bottom Ring)

- 3 F0 Horizontal LVDT

- 5 Accelerometers of 2 different types installed on F0:

- 3 Horizontal Accs

- 2 Vertical Accs

- 17 Coils of 3 different types

- 5 F0 Coils

- 8 Marionette Coils

- 4 Mirror Coils

- 3 Piezos on bottom ring (Not used yet)

- 19 Motors

- 1 Top screw F0 vertical motor

- 3 F0 trolley motors

- 4 Fishing rod motors

- 2 Marionette motors

- 4 F7 motors

- 5 Accelerometer motors

#### On detection (SDB1) superattenuator (OB) are installed:

- 9 LVDTs of 3 different types

- 6 Vertical LVDTs (F0, F4, F7 Crossbar, Bottom Ring)

- 3 F0 Horizontal LVDT

- 5 Accelerometers of 2 different types installed on F0:

- 3 Horizontal Accs

- 2 Vertical Accs

- 5 F0 Coils

- 3 Piezos on bottom ring (Not used yet)

- 18 Motors

- 1 Top screw F0 vertical motor

- 3 F0 trolley motors

- 3 Fishing rod motors

- 2 Marionette motors

- 4 F7 motors

- 5 Accelerometer motors

# Introduction Control system setup

Analog Front End **ADC** DAC **FPGA** PCle GbE DSP SRIO

10 Vpp, differential I/O

6ch ADC 24bit, up to 3.84 MSPS 6ch DAC 24bit, up to 640 kSPS

Analog and digital parts have been embedded in a single board.

2 lanes x Gen2 PCle (up to 10 Gbps)

Gigabit Ethernet - Control

Up to 12 modules per crate

4 lanes x SRIO (up to 20 Gbps)

RapidIO Switch

### Introduction Control system setup

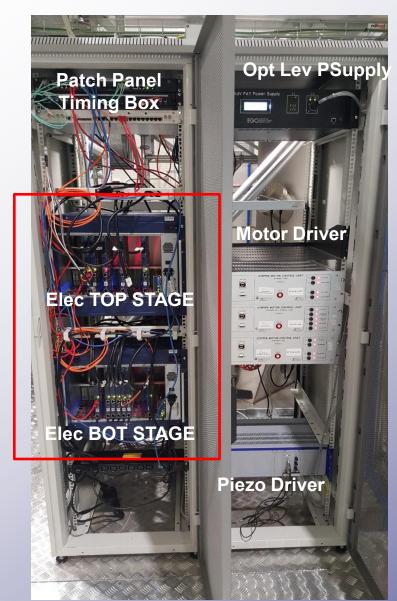

**NI Tower**

8

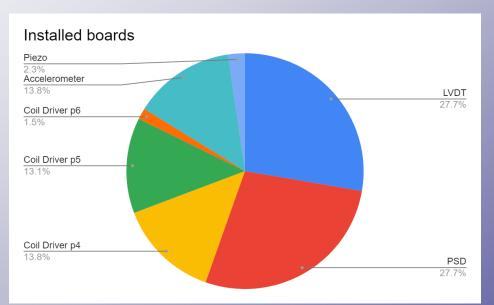

- There is a total of 130 DSP boards in SAT, PAY, INJ of 7 alternative configurations depending on their use:

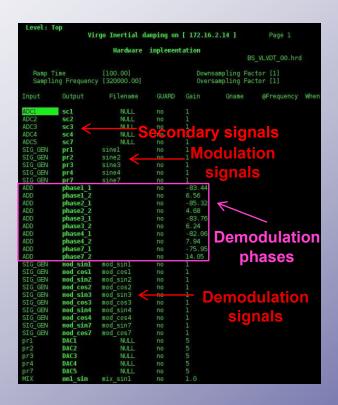

- LVDT: digital demodulation of horizontal and vertical LVDTs of F0 and F7.

- Accelerometer: LVDT digital demodulation and control of the sensing element of both horizontal and vertical F0 accelerometers.

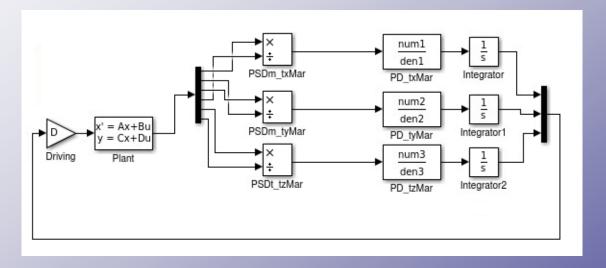

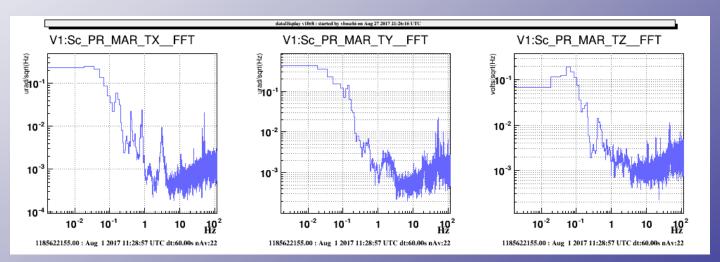

- PSD: signal acquisition of mirror (PSDf, PSDi) and marionette (PSDm, PSDt) optical lever PSDs.

- **Coil Driver p4**: the board is equipped with TI OPA544 operational amplifier and is used for F0 and F7 actuation. The opamp is capable of erogating a peak current of 310 mA.

- Coil Driver p5: the board is equipped with AD8397 operational amplifier and is used for mirror and marionette high power actuation. The opamp is capable of erogating a peak current of 2 A. This board type has been produced in limited quantities (20 samples).

- Coil Driver p6: the board is equipped with analog shaping filters, TI OPA1612 operational

amplifiers and it is used for NE and WE low noise mirror actuation. The opamp is capable of

erogating a peak current of 40 mA.

- Piezo: driving of bottom ring piezoelectric actuators.

| Electronic board name | Installed Boards | % (P <sub>i</sub> ) |

|-----------------------|------------------|---------------------|

| LVDT                  | 36               | 28                  |

| PSD                   | 36               | 28                  |

| Coil Driver p4        | 18               | 14                  |

| Coil Driver p5        | 17               | 13                  |

| Coil Driver p6        | 2                | 2                   |

| Accelerometer         | 18               | 14                  |

| Piezo                 | 3                | 2                   |

|                       |                  |                     |

|                       |                  |                     |

|                       |                  |                     |

| Total                 | 130              |                     |

## Introduction

Control system setup

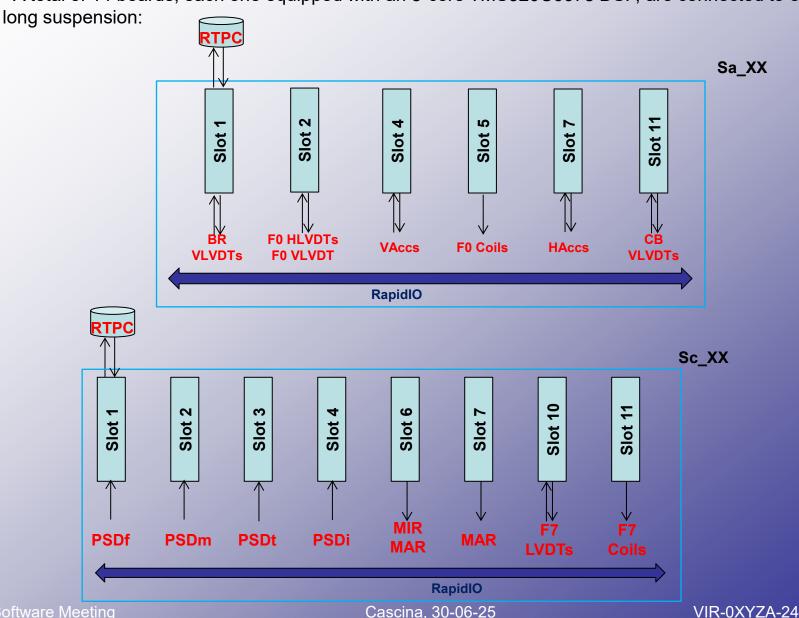

• A total of 14 boards, each one equipped with an 8-core TMS320C6678 DSP, are connected to each

#### SA control is an extremely complex system:

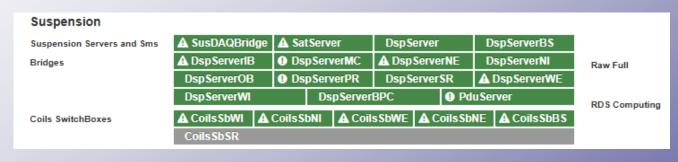

- 130 DSP boards are installed on BPC, BS, IB, MC, PR, NI, NE, WI, WE, SR, OB

- 185 control code files are running at the same time on the DSP cores at 10 kHz (IP, F7, LC controls), 40 kHz (Global signals oversampling) and 320 kHz (Digital demodulation of sensors)

- All the DSP software (code, generated assembler and binaries) is archived in an SVN repo that can be browsed: https://svn.ego-gw.it/svn/satsw/DSPCode Adv/

| SA    | BOARD IP     | CONNECTED DEVICES | SOFTWARE RUNNING (Core4, 10 kHz)                       | SOFTWARE RUNNING (Core1, 320 kHz)                 |

|-------|--------------|-------------------|--------------------------------------------------------|---------------------------------------------------|

| IPC . | 172.16.2.104 | PSD               | /virgoDev/Sa/DSPCode_Adv/BPC/BPC_PSD                   |                                                   |

| PC    | 172.16.2.141 | PIEZO             | /virgoDev/Sa/DSPCode_Adv/BPC/BPC_CD                    |                                                   |

| a_BS  | 172.16.2.62  | BR LVDTs          | /virgoDev/Sa/DSPCode_Adv/BS/LVDT/BS_MASTER             | /virgoDev/Sa/DSPCode_Adv/BS/LVDT/BS_BR_LVDT_Demod |

| a_BS  | 172.16.2.53  | FO LVDTs          | /virgoDev/Sa/DSPCode_Adv/BS/LVDT/BS_LVDT_HG_SRIO       | /virgoDev/Sa/DSPCode_Adv/BS/LVDT/BS_LVDT_HG2      |

| a_BS  | 172.16.2.32  | F0 VAccs          | /virgoDev/Sa/DSPCode_Adv/BS/Accs/BS_vAcc_LQG           | /virgoDev/Sa/DSPCode_Adv/BS/Accs/BS_vAcc_Demod    |

| a_BS  | 172.16.2.33  | FO Coils          | /virgoDev/Sa/DSPCode_Adv/BS/InertialDamping/BS_ID_Diag |                                                   |

| a_BS  | 172.16.2.133 | F0 HAccs          | /virgoDev/Sa/DSPCode_Adv/BS/Accs/BS_Acc_LQG            | /virgoDev/Sa/DSPCode_Adv/BS/Accs/BS_Acc_Demod     |

| a_BS  | 172.16.2.52  | F1-F7 VLVDTs      | /virgoDev/Sa/DSPCode_Adv/BS/LVDT/BS_VLVDT_SRIO         | /virgoDev/Sa/DSPCode_Adv/BS/LVDT/BS_VLVDT         |

| ic_BS | 172.16.2.80  | PSD               | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_PSDf                 |                                                   |

| ic_BS | 172.16.2.108 | PSD               | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_PSDm                 |                                                   |

| Sc_BS | 172.16.2.110 | PSD               | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_PSDt                 |                                                   |

| Sc_BS | 172.16.2.84  | PSD               | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_PSDi                 |                                                   |

| Sc_BS | 172.16.2.181 | MIR, MAR Coils    | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_Mir                  |                                                   |

| Sc_BS | 172.16.2.179 | MAR Coils         | /virgoDev/Sa/DSPCode_Adv/BS/LC/BS_Mar                  |                                                   |

| Sc_BS | 172.16.2.139 | F7 LVDT           | /virgoDev/Sa/DSPCode_Adv/BS/LVDT/BS_F7_LVDT            | /virgoDev/Sa/DSPCode_Adv/BS/LVDT/BS_F7_LVDT_Demod |

| Sc_BS | 172.16.2.120 | F7 Coils          | /virgoDev/Sa/DSPCode_Adv/BS/F7/BS_F7_CD                |                                                   |

| Sa_IB | 172.16.2.28  | BR LVDTs          | /virgoDev/Sa/DSPCode_Adv/IB/LVDT/IB_MASTER             | /virgoDev/Sa/DSPCode_Adv/IB/LVDT/IB_BR_LVDT_Demod |

| Sa_IB | 172.16.2.130 | FO, F4, F7 LVDTs  | /virgoDev/Sa/DSPCode_Adv/IB/LVDT/IB_LVDT               | /virgoDev/Sa/DSPCode_Adv/IB/LVDT/IB_LVDT_Demod    |

| Sa IB | 172.16.2.9   | F0 VAccs          | /virgoDev/Sa/DSPCode_Adv/IB/Accs/IB_vAcc_LQG           | /virgoDev/Sa/DSPCode_Adv/IB/Accs/IB_vAcc_Demod    |

| Sa IB | 172.16.2.121 | FO Coils          | /virgoDev/Sa/DSPCode_Adv/IB/InertialDamping/IB_ID_Diag |                                                   |

| Sa IB | 172.16.2.23  | F0 HAccs          | /virgoDev/Sa/DSPCode_Adv/IB/Accs/IB_Acc_LQG            | /virgoDev/Sa/DSPCode_Adv/IB/Accs/IB_Acc_Demod     |

| Sc IB | 172.16.2.118 | PSD               | /virgoDev/Sa/DSPCode Adv/IB/LC/IB PSDf                 |                                                   |

| Sc IB | 172.16.2.86  | PSD               | /virgoDev/Sa/DSPCode_Adv/IB/LC/IB_PSDi                 |                                                   |

| SC IB | 172.16.2.107 | PSD               | /virgoDev/Sa/DSPCode Adv/IB/LC/IB PSDt                 |                                                   |

| SC IB | 172.16.2.173 | MAR Coils         | /virgoDev/Sa/DSPCode Adv/IB/LC/IB Mar1                 |                                                   |

| Sc_IB | 172.16.2.174 | MAR Coils         | /virgoDev/Sa/DSPCode_Adv/IB/LC/IB_Mar2                 |                                                   |

| Sa_MC | 172.16.2.128 | BR LVDTs          | /virgoDev/Sa/DSPCode_Adv/MC/LVDT/MC_MASTER             | /virgoDev/Sa/DSPCode_Adv/MC/LVDT/MC_BR_LVDT_Demod |

| Sa_MC | 172.16.2.51  | FO, F4, F7 LVDTs  | /virgoDev/Sa/DSPCode_Adv/MC/LVDT/MC_LVDT               | /virgoDev/Sa/DSPCode_Adv/MC/LVDT/MC_LVDT_Demod    |

| Sa_MC | 172.16.2.158 | FO VACCS          | /virgoDev/Sa/DSPCode_Adv/MC/Accs/MC_vAcc_LQG           | /virgoDev/Sa/DSPCode_Adv/MC/Accs/MC_vAcc_Demod    |

|       | 172.16.2.103 | FO Coils          | /virgoDev/Sa/DSPCode_Adv/MC/InertialDamping/MC_ID_Diag |                                                   |

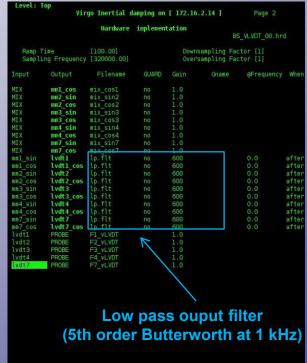

| Sa_MC | 172.16.2.14  | F0 HAccs          | /virgoDev/Sa/DSPCode_Adv/MC/Accs/MC_Acc_LQG            | /virgoDev/Sa/DSPCode_Adv/MC/Accs/MC_Acc_Demod     |

|       | 172.16.2.150 | PIEZO             | /virgoDev/Sa/DSPCode_Adv/MC/Tilt/Piezo_Test            |                                                   |

| Sc_MC | 172.16.2.101 | PSD               | /virgoDev/Sa/DSPCode_Adv/MC/LC/MC_PSDf                 |                                                   |

|       | 172.16.2.168 | PSD               | /virgoDev/Sa/DSPCode_Adv/MC/LC/MC_PSDi                 |                                                   |

| Sc_MC | 172.16.2.88  | PSD               | /virgoDev/Sa/DSPCode_Adv/MC/LC/MC_PSDTf                |                                                   |

| Sc_MC | 172.16.2.109 | PSD               | /virgoDev/Sa/DSPCode_Adv/MC/LC/MC_PSDTi                |                                                   |

| Sc_MC | 172.16.2.171 | MAR Coils         | /virgoDev/Sa/DSPCode_Adv/MC/LC/MC_Mar1                 |                                                   |

| Sc_MC | 172.16.2.172 | MAR Coils         | /virgoDev/Sa/DSPCode_Adv/MC/LC/MC_Mar2                 |                                                   |

| Sc_MC | 172.16.2.176 | MIR Coils         | /virgoDev/Sa/DSPCode_Adv/MC/LC/MC_Mir                  |                                                   |

| Sa_NE | 172.16.2.37  | BR LVDTs          | /virgoDev/Sa/DSPCode_Adv/NE/LVDT/NE_MASTER             | /virgoDev/Sa/DSPCode_Adv/NE/LVDT/NE_BR_LVDT_Demod |

| Sa NE | 172.16.2.40  | FO LVDTs          | /virgoDev/Sa/DSPCode Adv/NE/LVDT/NE_LVDT               | /virgoDev/Sa/DSPCode Adv/NE/LVDT/NE LVDT Demod    |

- There are 18 LVDTs installed on long tower suspensions of 3 different types

- 9 Vertical LVDTs (F0 F7 Crossbar, Bottom Ring)

- 3 F0 Horizontal LVDT

- 6 F7 LVDTs

- Each sensors have been characterized and calibrated

- All the LVDTs are operated using a digital demodulation scheme at 320 kHz sampling frequency:

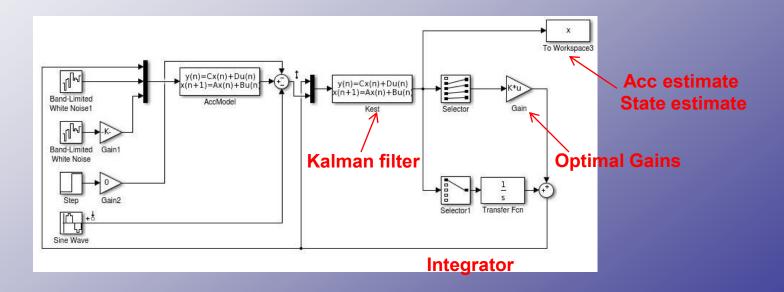

- There is a total of 5 Accelerometer (Accs) installed on the suspension F0 of 2 different types

- 3 Horizontal Accs

- 2 Vertical Accs

- A model of the sensor mechanics and its disturbances has been developed in order to design the Kalman estimator and the controller.

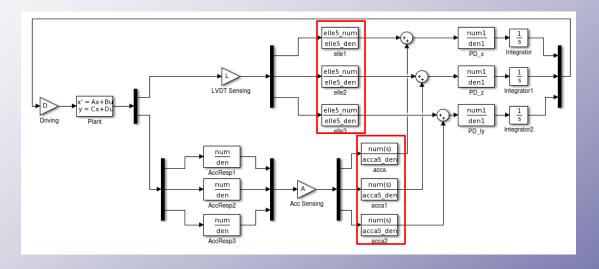

## Inertial Damping Overview

Two loops based on traditional sensor blending are currently used to control IP motion:

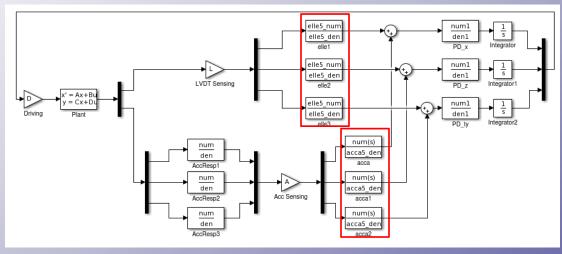

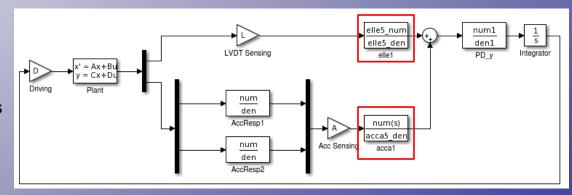

#### **Horizontal Inertial Damping (ty, x, z)**

6 x 3 plant matrix: (3 LVDTs + 3 Accelerometers) x 3 Coils on filter 0

3 x 3 Diagonalized Control matrix

#### **Blending filters**

#### **Vertical Inertial Damping (y)**

3 x 2 control matrix: (1 LVDTs + 2 Accelerometers) x 2 Coils on filter 0

1 x 2 Diagonalized Control matrix

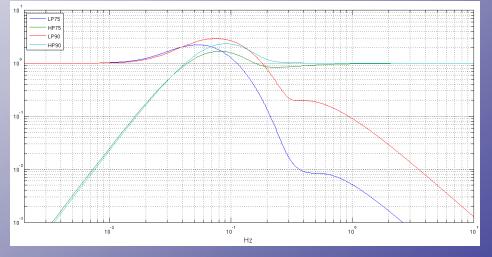

# Inertial Damping Standard Blending

Two Accelerometer-LVDT blending filters are used (High Pass for Accs and Low Pass for LVDTs)

- 75 mHz crossover frequency used for standard operation

- 90 mHz crossover frequency for robustness (High microseism or windy conditions)

**Standard Blending filters**

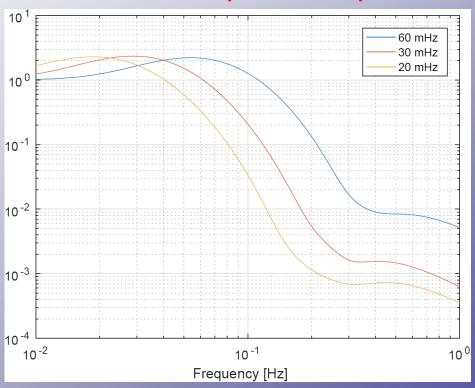

## Inertial Damping

- Global Inverted Pendulum Control (GIPC) is a technique already used in VIRGO in which common and differential error signals are used to control the IP top stage instead of the local LVDTs and Accelerometers

- Using this strategy the crossover frequency of the blending filters can be lowered (20 mHz, 30 mHz) without losing robustness improving the rejection of microseism.

#### **Accelerometer low-pass filter comparison**

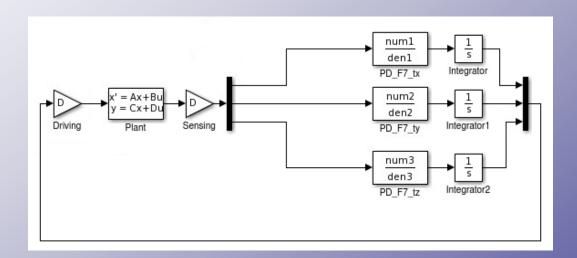

### **F7 Control**

3 PID Filters are now used for the F7 control of all long suspensions.

#### F7 Control (tx, ty, tz)

6 x 6 plant matrix: 6 LVDTs x 6 Coils on the F7

3 x 3 Diagonalized Control Matrix

• Tx and Tz filters are required to damp a 400 mHz payload mode.

### **Local Control**

#### Local Control (tx, ty, tz)

3 x 8 plant matrix:

3 PSD signals x 8 Coils on Marionette

3 x 3 Diagonalized Control Matrix

Bang-bang control (Coarse) PID (Fine)

A few nrad/sqrt(Hz) of spectral diplacement above 1 Hz

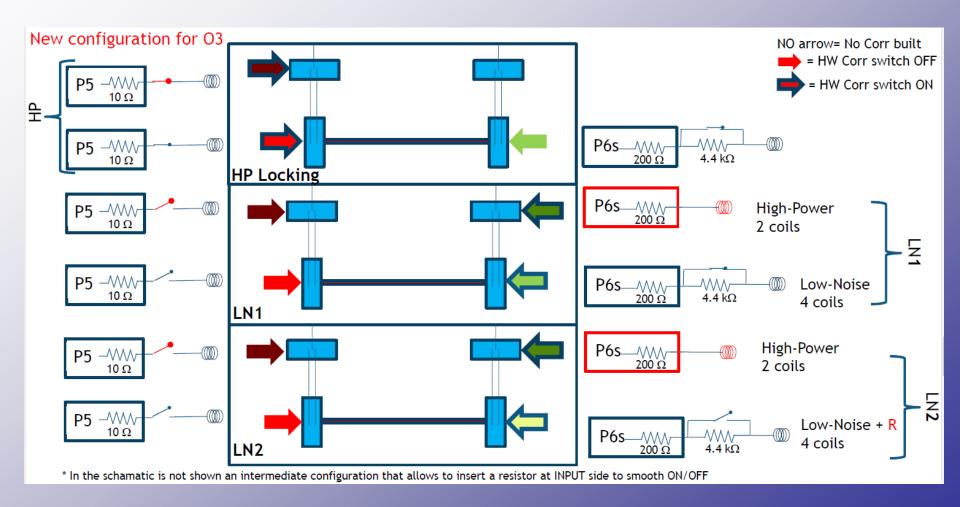

### Locking

Three mirror actuation modes are used:

- High power (10 Ohm output resistance) for lock acquisition only

- Low Noise 1 (200 Ohm output resistance + 1st order shaping filter)

- Low Noise 2 (4.6 kOhm output resistance + 1st order shaping filter)

### **Supervisor**

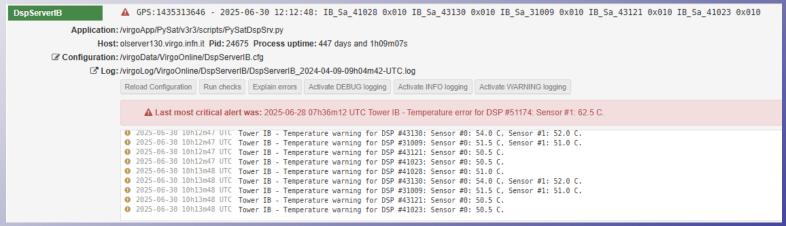

- Supervisor is an important part of the subsystem since it allows to monitor the status of both and hardware and software and to interact with the DSP from external code such as Python.

- SAT Supervising software used in O2 and O3 was based on TANGO. However, it was extremely complex to maintain and unstable.

- The supervisor has been fully re-written by Akis with more functionality, less complexity and more stability.

### Thank you for your attention!!